功率半导体赛道火热,尤其受到电动汽车与能源行业的热烈追捧。那么,如何确保功率半导体的性能呢?关键在于精准测试。NI将在SEMICON(NI 展位号:N4馆N4356)展示其最新功率半导体测试方案,现场还可与SET技术工程师交流。

WBG半导体可靠度测试H3TRB专区

对于H3TRB动态测试,SET提供的系统可将行业的扩展要求转化为自动动态测试。系统特别注重灵活性,以便能够快速满足不断变化的要求。

测试类型

动态 H3TRB/ DRB 测试系统

测量技术

◆每个系统80-240个被测设备(80个被测设备1个高压电源)

◆0V至1500V;4A,用于80DUT

◆单个DUT泄漏电流测量(静态H3TRB期间)

80个测量通道

◆通过关闭开关提供单个DUT过流保护

基于硬件的单个DUT快速关断,应力阶段为65mA±20%,读出阶段为650μA±20

◆单DUT电压控制

主动电压控制可将负载电压补偿至<±0.5V

动态测试输出级

◆最大输出电压高达1500V

◆输出频率可在0Hz至500kHz之间配置(最大频率取决于电压和DUT电容)

◆占空比在25%至75%之间可变,每5%为一档

软件和测试程序

◆全自动测试程序

◆测量数据保存在tdms文件中

◆基于NILabVIEW和TestStand的软件

安全

◆用软件连接和评估试验箱的外部安全锁

◆高压插头连接的安全电压监控

◆高压供电设备的安全释放

最新一代功率半导体SiC凭借其在禁带宽度和热导率等方面的优势,成功击中高功率高能效应用需求。SiC测试有何挑战与应对方法?以下技术文章介绍了使用动态栅极应力(Dynamic Gate Stress, DGS)测试过程对基于SiC的功率半导体进行新型可靠性测试的意义。相信您看完会受到启发。

文章作者:艾默生测试与测量业务集团-NI旗下公司SET GmbH半导体研究主管 Gabriel Lieser

碳化硅(SiC)组件拥有众多技术优势,适用于要求严格的应用。但硅(Si)组件和SiC组件之间存在结构差异,该差异会影响可靠性测试。

SiC(碳化硅)因其诸多出色性能成为半导体市场的重要材料。SiC的电气击穿电压高于硅,因此可以提升组件的性能和效率。SiC还支持在更高温度下运行,这样更有利于散热,并可在更小的空间内实现更出色的性能。由于SiC具有高导热性,使组件在严苛条件下也可高效运行。SiC组件的高开关频率支持更小巧轻便的设计,这一点作为主要优势使其可用于众多应用。得益于上述特性,SiC涉及的应用行业日益广泛,如电动汽车、可再生能源、工业驱动技术和航空航天。

SiC功率半导体需要新的可靠性测试

尽管SiC的应用前景广阔,但仍需要针对基于SiC的新组件开发特定的可靠性测试。由于SiC和硅之间存在结构差异,无法使用现有的硅组件测试方法和假设条件。SiC的晶体结构与硅不同,因此具有不同的电学和热学性能。如果忽略这些差异,则可能无法检测组件的潜在生命周期或性能弱点。本文介绍了使用动态栅极应力(Dynamic Gate Stress, DGS)测试过程对基于SiC的功率半导体进行新型可靠性测试的意义。

DGS测试主要用于SiC-FET(场效应晶体管)。在测试过程中,向DUT(待测设备)的栅极以方波信号形式施加应力信号,该信号使用DUT的最大和最小栅极电压。应力循环期间,采用主动温度控制将DUT调整至所需的应力温度。按照规定时间间隔暂停施加应力,以测量DUT的栅极阈值电压和RDSon。

对于宽带隙半导体测试过程,动态应力法和静态应力法之间存在显著差异。本文所述的测试过程采用SET GmbH的测试系统。使用该测试装置对测试规范做出准确解释,并将测量结果与实际应用进行比较。正确的测量过程对获得可靠且可重复的测量结果同样重要。测试相关内容可参考ECPE(欧洲电力电子中心)指南AQG 324,其中为欧洲SiC组件的新测试过程提供了实践规范和指南。

动态栅极应力(DGS)测试:功能原理和测量过程

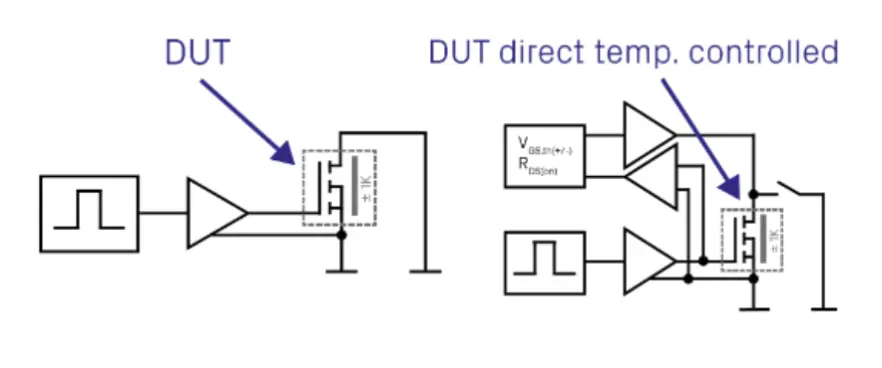

在DGS测试过程中,FET将其漏极和源极接点处连接至地电位,并在其栅极接点处施加应力(图1)。施加的应力信号定义请参见AQG324指南。应力信号参数如下:方波信号的幅值是所需DUT规格所允许的最大负电压和正电压。DUT的上升时间(dV/dt)应为1V/ns左右,应力频率应大于或等于50 kHz,占空比范围为20%至80%。

图1:DGS测试的测试设置:左侧为应力电路,右侧为测量电路。

应力的持续时间由频率决定,因此频率越高测试时间越短。根据指南AQG324的规定,应力持续时间应不小于10^11个周期。测试温度应主动调节且严格控制在25 °C。

作为该测试过程的一部分,在全自动应力暂停期间对栅极阈值电压和RDSon电阻进行测量。精确测量和适当预处理在测试过程中非常重要。预处理用于确保每次测量时测试对象的条件相同,从而保证测量结果具有可比性。本文中的指南AQG引用了JEDEC指南JEP184,其中介绍了正确的测量过程。栅极定义电压应与建议的栅极-源极有效电压或允许的最大/最小栅极-源极电压相对应。

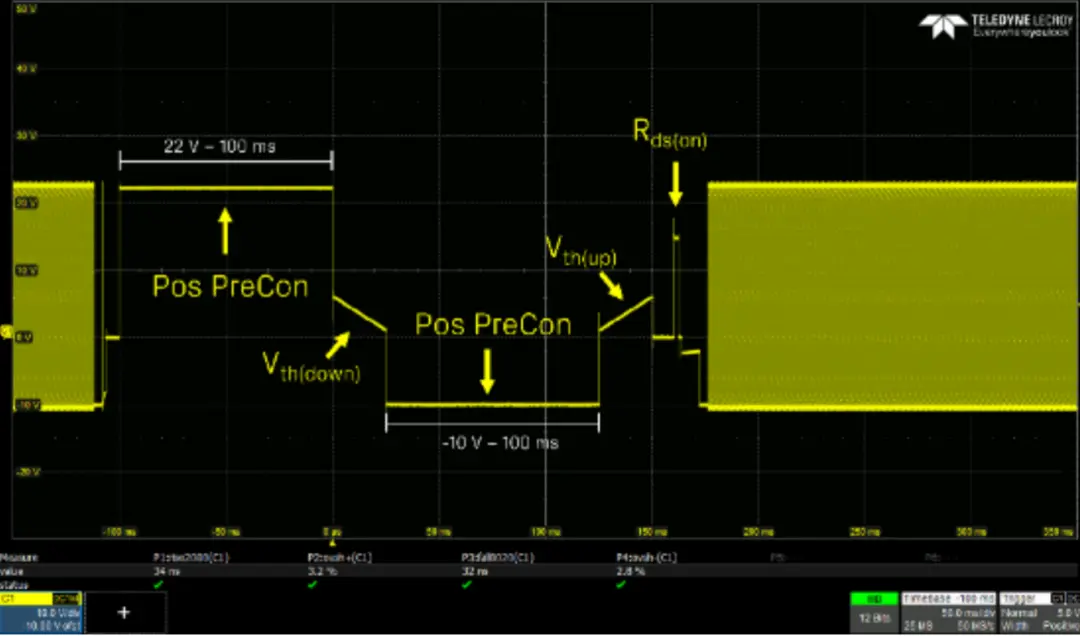

常见的预处理时间为100ms,但有时也会明显延长。预处理完成后,应快速测量栅极阈值电压,根据指南建议测量应在10ms内进行。此处所示的示波器记录结果由SETGmbH的DGS系统完成,用于说明测量过程。

图2中的曲线与栅极信号相对应。开始时,可以观察到300kHz下-10V~+22V 的应力施加阶段,随后在测量过程开始时暂停。

测量过程从+22V预处理脉冲开始,该脉冲持续100ms。随后,栅极电压以非常小的步长持续变化。在测试阶段,将测量漏极电流Idrain并将其设置为特定值,例如20mA。由于FET已打开,因此在“Vth(down)”测试阶段开始时,有20mA电流流过。一旦栅极电压接近阈值电压,FET就会缓慢关闭,之前可完全通过FET的电流会缓慢减小。当Idrain电流达到定义值(例如10mA)时,栅极电压保存为Vth(down)。对电压负值区域重复相同的测量步骤:最小栅极电压-10V持续100ms。 然后栅极电压逐渐增加,在10mA处保存Vth(up)电压。

图2:测量期间DGS系统的栅极信号

Vth测量完成后,测量测试对象的Rds(on)电阻。为此,在漏极和源极之间产生可调电流脉冲。通过测量漏极和源极之间的电压降来确定Rds(on)电阻。完成这些测量后,继续进行动态栅极应力测试。可靠实施该过程对准确表征SiC半导体在应力下的行为并保障其可靠性至关重要。

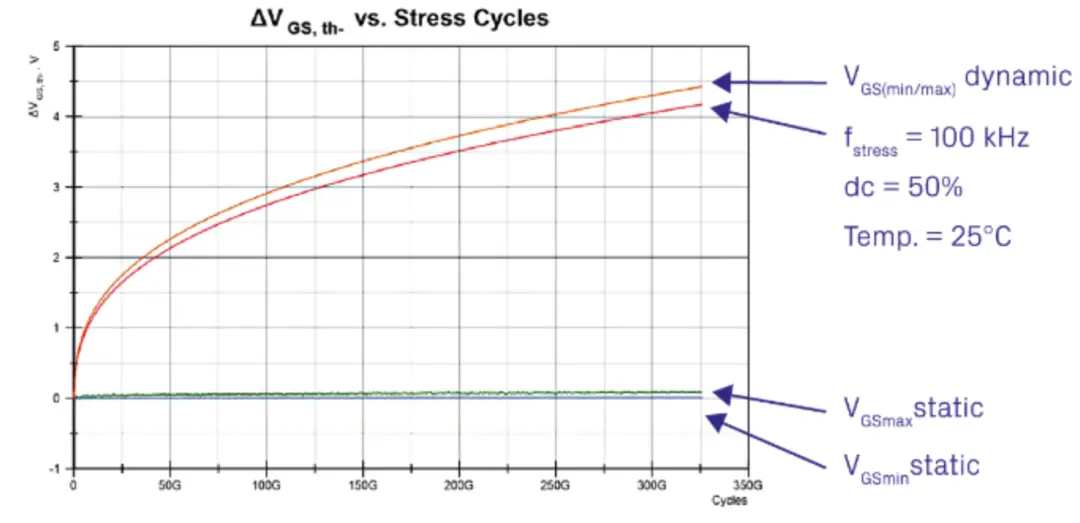

DGS测量结果与静态测量结果的比较

为评估DGS测试的必要性并将其与传统静态测试过程进行比较,进行了大量比较试验。使用RDSon为80mΩ的常规1200V SiC MOSFET为测试对象。该过程使用的MOSFET均为最新一代产品,目前已在公开市场上销售。使用数据表中在100kHz应力频率和50%占空比下的最大建议栅极电压作为以下测试的应力参数。整个测试过程均在稳定的25 °C实验室条件下进行。

对所得数据的分析表明,静态和动态测试过程之间存在巨大差异(图3)。

图3:动态和静态栅极应力测量结果的比较

根据图形可知二者差异显著,特别在栅极阈值电压漂移方面。动态测试中,经过300千兆周期后,栅极阈值电压出现大于4V的明显漂移。而静态测试中未观察到这种漂移效应。标准MOSFET的漂移约为0.5 V,而动态测试中的漂移较正常值高出7倍。对于多数电路而言,这种电压升高可能会导致性能显著下降甚至电路故障。SET GmbH在动态测试中多次识别到这些偏差; 但在静态测试中未发现此类漂移。

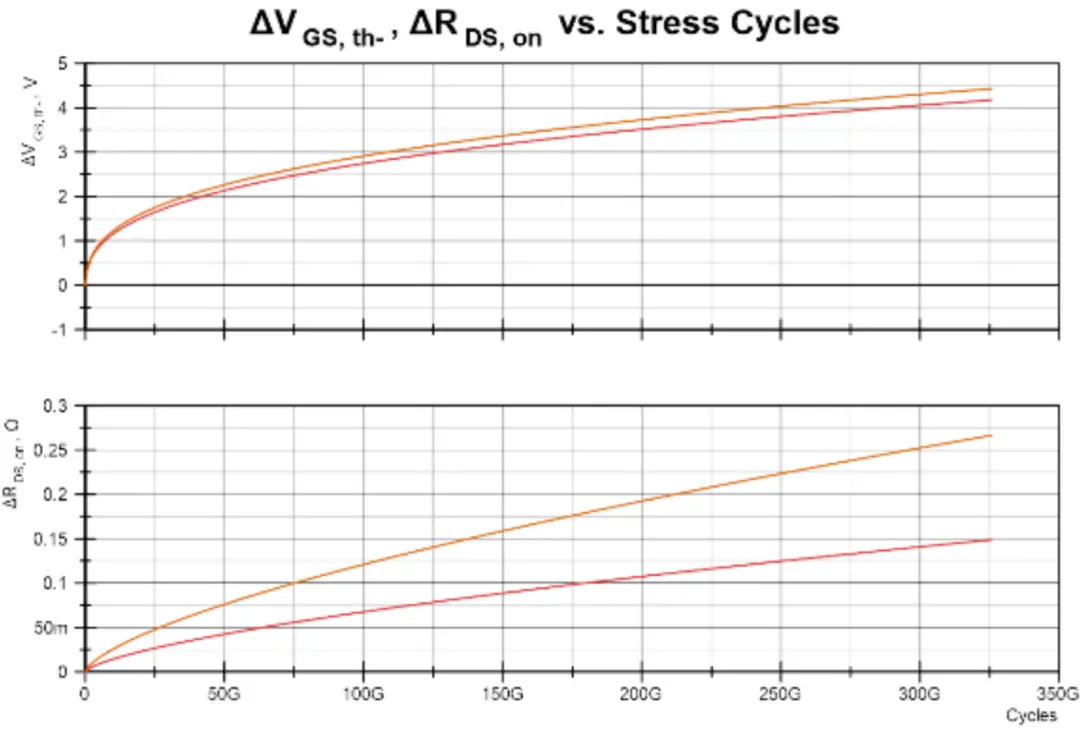

此外,进一步研究了栅极阈值电压的变化与RDSon电阻之间的关系。图4则基于图3中第一次测试的测量结果,明确说明了阈值电压漂移和RDSon电阻之间的关系。可以假设,当栅极阈值电压发生漂移时,RDSon电阻也会根据组件的特性数据曲线而变化。这一关系会在运行过程中影响组件效率,因此,也会对电动汽车行驶里程等实际应用造成影响。根据测试期间的连续测量结果来估计工作条件下的具体影响。

图4:DUT的阈值电压与Rds(on)电阻之间的相关性

为不断加深对SiC功率半导体现象的理解,应继续进一步发展DGS测试和所有其他动态测试过程。特别是对于长期分析的建模,应收集尽可能多的数据,以便开发可靠的功率半导体来应对未来的挑战。

来源:恩艾NI知道