从表 1 中可以看到,除了调制解调器是用于上网和通话之外,智能座舱 SoC 已经囊括了几乎所有的关键算力单元。随着市场对座舱性能要求的持续提高,这些算力单元的处理能力也必将得到进一步的增强。

1.2 座舱算力需求分解

智能座舱在显示、视觉、音频等多个领域的主要应用依赖于座舱 SoC 中各计算单元的紧密配合与高效协作。表 2 简要总结了 SoC 的算力分解情况。

表 2 座舱 SoC 算力分解

功能特性SoC 组成说明中控娱乐屏CPU 、GPU、DPUCPU 负责运行操作系统,进行整体系统的控制和应用程序的管理,并处理触摸屏的点击。GPU 负责图形渲染和图像处理。DPU 负责管理和控制显示设备的输出多媒体音视频播放CPU 、GPU、VPU 、DPUCPU 、GPU 、DPU 承担的工作与中控娱乐屏中的一样,VPU 则作为硬件加速器,负责视频编/ 解码和图像处理任务,可提高系统性能,减轻CPU 负担流媒体后视镜CPU 、ISP、DPUCPU 用于整体系统的控制,DPU 负责显示输出,ISP 负责将从图像传感器获取的原始图像数据进行处理和优化,提供高质量的图像抬头显示器CPU 、GPU、DPUCPU 负责运行操作系统、导航软件,通过接收导航数据,解算车辆运行姿态并生成道路航向信息。GPU 负责图形渲染和图像处理,如果是AR-HUD,还需负责运行AR 3D 引擎。DPU 负责管理和控制显示设备的输出乘客感知系统CPU 、ISP、NPUCPU 负责整体系统控制;ISP 负责从图像传感器获取原始数据,生成高质量的图像;NPU 负责通过深度学习方式生成感知结果语音交互系统CPU 、Audio DSP 、NPUCPU 负责运行操作系统,并处理音频数据的输入和输出;Audio DSP 负责运行各类音频处理算法,提供可用的音频数据;NPU 负责执行语音识别、自然语言处理、对话管理,以及生成响应结果

#02CPU 算力评估

在座舱 SoC 的所有算力单元中,CPU 无疑占据着举足轻重的地位。甚至可以说,有经验的工程师只需了解一颗 SoC 所采用的 CPU 类型,就能大致预测出这颗 SoC 的性能上限。这是因为 CPU 作为核心处理单元,对整体性能起着决定性的作用。

2.1 CPU 性能评估公式

CPU 是计算机系统的核心组件,负责运算和系统控制。它是信息处理及程序运行的关键执行单元,掌控着系统内的所有资源,如存储器、输入 / 输出通道、数据处理以及逻辑计算等。

对智能座舱用户来说,最直观的感受就是车机系统运行应用程序的响应速度。而这个响应速度,最直接的体现就是 CPU 执行程序的时间。

1. 影响 CPU 性能的因素

我们都知道,CPU 在执行任务时需要依赖时钟,时钟掌控着每条指令在 CPU 流水线中的执行节奏。因此,时钟周期的长短,或者称为“滴答数”,就显得尤为重要,通常用时钟频率来表示这一指标,其单位是 Hz,即时钟周期的倒数。例如,如果某 CPU 的时钟频率为 1GHz,那么它的时钟周期就是 1s/(1 × 10^6) ,即 1ns。

对于 CPU 执行一段程序所消耗的时间,可以使用一个公式来表示:

程序的CPU执行时间 = 程序的CPU时钟周期数×时钟周期

一段要执行的程序,首先要由编译器生成指令。所生成的总程序指令数被称为 IC(Instruction Counter,指令计数)。假设执行每条指令的时钟周期平均数为 CPI(Clock Cycle per Instruction),那么程序的 CPU 时钟周期数就可以按如下公式来进行计算:

程序的CPU时钟周期数 = IC× CPI

现在,我们可以使用 IC 和 CPI ,以及时钟周期来写出基本的性能公式:

CPU时间 = IC × CPI× 时钟周期

或者

表 3 总结了影响 CPU 性能的构成因素,以及如何测量这些关键因素。

表 3 CPU 性能因素

根据表 3 所总结的信息,我们可以用 IC、CPI 和时钟周期这三个参数来评估 CPU 的性能, 进而得出用户可感知的 CPU 执行时间。CPU 时间是衡量计算机性能的全面且可靠的指标。而 IC、CPI 和时钟周期这三个参数是相互影响的,不能单独用其中一个因素来全面衡量 CPU 的性能。

例如,如果我们修改指令集架构,使用采用了 CISC(复杂指令集)的 CPU,那么对于同一段程序而言,编译器生成的指令数可能会减少。然而,在 CPU 的微架构设计中,采用复杂指令可能会导致 CPI 和时钟频率的增加。这样一来,指令数量减少所带来的性能提升可能会被抵消,甚至可能产生负面影响。因此,我们需要综合考虑这三个参数,才能更准确地评估 CPU 的性能。

2. 影响程序性能的因素

程序的性能受到多方面因素的影响,包括算法、编程语言、编译器、指令集架构以及硬件微架构设计。表4 简要概述了这些因素是如何具体影响 CPU 性能公式中的各个参数的。

表4 影响程序性能的因素

2.2 CPU 性能基准测试

针对智能座舱 SoC 的 CPU 性能评估,我们需要使用一个直观和便于理解的评价标准,以便于横向比较各家 SoC 的能力。这其中,有一些人们常用的标准。

1. DMIPS 标准

在评估 CPU算力时,大部分厂商会使用DMIPS这个衡量参数。DMIPS(DhrystoneMillion InstructionsexecutedPerSecond),意思是在CPU上运行Dhrystone测试程序,每秒能够执行的百万指令数。例如,最新的高通8295 座舱SoC,其CPU 号称可达220k DMIPS 算力,意思是每秒可以执行220 000 000 000 条Dhrystone指令。

Dhrystone 被称为合成测试基准程序,它主要用来评估处理器在执行整数和逻辑运算时的性能。Dhrystone 包含了多种整型语句和逻辑语句的循环,这些循环涉及各种赋值操作、数据类型及区域、控制流指令、过程调用、参数传递以及整数逻辑运算等。通过这些测试,可以对处理器在执行这类操作时的性能有全面了解。

然而,正因为 Dhrystone 主要关注整型和逻辑运算,所以仅凭 DMIPS 测试结果并不能表明 CPU 的整体算力。特别是当涉及浮点运算、内存访问速度、I/O 性能等其他关键因素时,Dhrystone 的测试结果就显得不够全面了。在这种情况下,有必要引入另外一种标准化的算力衡量方法。

2. 关于合成测试基准程序的说明

在《计算机体系结构:量化研究方法》一书中,两位作者 John.L.Hennessy 和 David A.Patterson 非常详细地阐述了 CPU 算力衡量的方法。

在测量计算机性能时,采用实际的应用程序进行基准测试被认为是最佳实践。这是因为简单的合成基准测试程序,如 Dhrystone,虽然易于实施和比较,但可能无法真实反映复杂应用程序的性能表现。其原因在于:

( 1 )性能隐患与合成基准测试的局限性

通常合成基准测试远比实际应用程序简单。因此,它们可能无法全面揭示处理器在处理复杂任务时的性能。编译器的编写人员和架构师可能通过优化特定程序来优化,使得计算机在执行这些简单程序时表现得更快,而这并不代表程序在实际应用中的性能。

(2)编译器的优化与专有标志的问题

为了在 Dhrystone 等基准测试中取得好成绩,编译器的编写者可能会使用专有标志对程序进行特定优化。这些优化虽然提高了测试分数,但可能引发其他程序的非法转换或性能损耗,因为其本质是服务测试,而非通用性能增强。

为了确保测试的公平性,需在测试的标准化和源代码修改方面进行约束。

1 )测试人员通常要求使用相同的编译器(如 GCC 或 LLVM)和统一的编译标志。这样做可以减少因编译器差异或优化标志不同而导致的性能测量误差。

2)允许修改源代码可能会导致测试结果的偏差,因为优化可能只针对特定测试而非实际应用场景。通常,对源代码的修改应该受到限制或完全禁止,以保持测试的公正性。

3. SPEC 基准测试程序

基准测试应用程序集(基准测试套件)是性能评估的重要工具,在设计时尽可能接近实际应用程序,以便更准确地衡量处理器在处理不同类型任务时的能力。这些套件包含了多个基准测试,每个测试都针对特定的性能方面,如 CPU 单核 / 多核计算能力、内存访问速度、I/O 性能等。通过使用这样的套件,可以获得处理器在多种应用场景下的综合性能表现。

在众多基准测试套件之中,SPEC(标准性能评估组织)的系列套件堪称典范,自 SPEC89 起不断进化到 SPEC2017。其中,用于 CPU 测试的为 SPEC CPU2017 基准测试程序。

SPEC CPU2017由43 个基准测试程序组成,分为20 个整型和23 个浮点基准测试程序。整型和浮点类基准测试程序又依据吞吐量和速度进行了细分,即将43 个测试程序分为整型吞吐量(SPECrate2017INT)、整型速度(SPECspeed2017INT)、浮点吞吐量(SPECrate2017FP)、浮点速度(SPECspeed2017FP)4 个类别。

其中,SPECspeed 类型用于 CPU单核的测试;SPECrate 类型用于 CPU 多核测试,即测试多个副本进程。测试值越大,表示时间越短,CPU 处理能力越高。表 5 和表 6 分别按整型和浮点分类标准,整理了 SPEC 2017 测试程序的说明。

表 5 SPEC 2017 整型测试程序的说明

SPECrate 2017 INT

SPECspeed 2017 INT编程语言千行代码数应用场景500.perlbench_r600.perlbench_sC362Perl 编程语言解释器502.gcc_r602.gcc_sC1304GNU C编译器505.mcf_r605.mcf_sC3路径规划520.omnetpp_r620.omnetpp_sC++134使用离散事件模拟技术来模拟和分析计算机网络的行为和性能523.xalancbmk_r623.xalancbmk_sC++520XSLT 将XML转换为HTML525.x264_r625.x264_sC96视频压缩531.deepsjeng_r631.deepsjeng_sC++10Alpha-beta 树搜索(如在模拟国际象棋游戏中的应用)541.leela_r641.leela_sC++21蒙特卡洛树搜索(在围棋游戏中的应用)548.exchange2_r648.exchange2_sFortran1递归式解决方案发生器(在数独游戏中的 应用)557.xz_r657.xz_sC33通用数据压缩

表 6 SPEC 2017 浮点测试程序的说明

544.nab_r

644.nab_sC24分子动力学549.fotonik3d_r649.fotonik3d_sFortran14计算电磁学554.roms_r654.roms_sFortran210区域海洋气候建模

从表 5 和表 6 可以看出,SPEC CPU2017 基准测试是一些实际的应用程序,它们经过简单修改就可以移植到不同架构的 CPU 上运行,并能在最大程度上降低 I/O 对性能的影响。

4. SPEC 基准测试结果

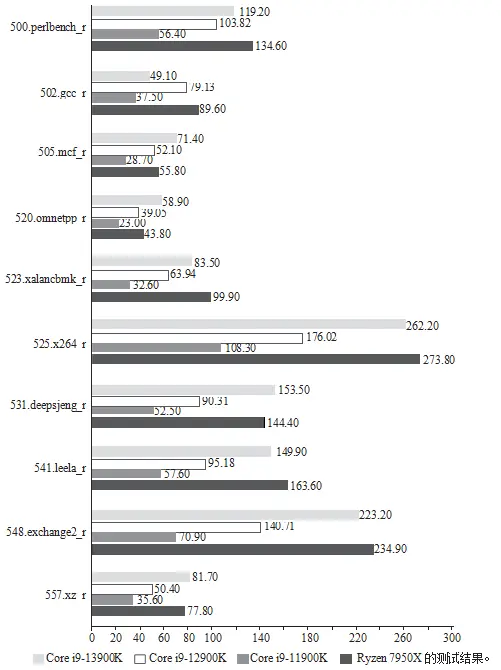

使用 SPEC基准测试程序套件,可以横向对比不同的CPU,得到可比性较强的测试结果。图1引用了AnandTech网站对Inteli9系列芯片和AMDRyzen7950x 芯片所做的评测,读者从中可以看到相关的测试结果。

图 1 SPECrate(多核测试)整型和浮点测试对比结果

图 1 采用直方图形式,可以直观地比较4 种类型CPU在多核测试条件下的各种测试表现。比如,在各种测试中,AMD公司的Ryzen7950x和Intel公司的Corei9-13900K 芯片性能相当。而Intel的Corei9-11900K的性能指标几乎总是最低的。

来源:汽车电子与软件 作者:张慧敏